LSI設計の言語とは?

Bluespecが選ばれてきた理由

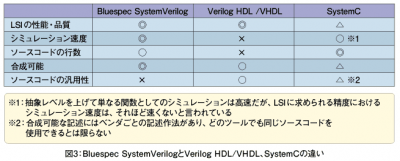

そのほかのBluespec SystemVerilogの特徴として、すべて合成可能、ということが挙げられます。合成可能とは、実際のLSIの機能として実装できることを意味しています。従来のVerilog HDLなどの言語において、シミュレーションのために用意された構文などは合成可能ではありませんでしたが、Bluespec SystemVerilogではテストベンチなどすべてが合成可能なVerilog HDLに変換されます。このことは、プロトタイプシステムやエミュレータと呼ばれる高速な検証システムの利用を促進することにつながります。

このようなメリットによって、さまざまなLSIのプロジェクトにBluespec SystemVerilogが使用されてきました。公開(http://csg.csail.mit.edu/pubs/publications.html)されているものとしては、MITのCSAILにおけるプロセッサやH.264デコーダなどが有名です。

一方、現在はシステムレベル設計の黎明(れいめい)期ということもあり、Bluespec SystemVerilog以外にもさまざまな言語が提唱されています。中でもSystemCはクラスライブラリを提供することでC++言語をLSI設計へ適用できるようにしたもので、日本においても数多くのユーザーが存在します。LSIとソフトウエアの協調シミュレーションなど、シミュレーションにおいての優位性があります。

ただし、LSIの特徴である一度に複数のモジュールが実行される、いわゆる並列性を記述したり、LSIに求められる細かいタイミング調整などを記述したりするためにはRTLと同等の詳細さでソースコードを記述する必要があるなど、実際のLSI設計への適用には課題があります。

ソフトウエアにおいては、特定のアプリケーションではアセンブラが使用されるケースもありますが、ほとんどはC++、Javaのような高級言語以降の言語へと置き換えられました。同様にBluespec SystemVerilogは、既存のVerilog HDLを代替することを目指しています。特にほかのシステムレベル設計言語と異なり、プロセッサなどの複雑なデータパス、制御系と言われる分野の事例が豊富で、次世代のHDLであると期待されています。

Bluespec SystemVerilogを始めるには

Bluespec社は、このBluespec SystemVerilogをIEEE標準化への働きかけを行っており、Bluespec以外のベンダからも、さまざまなツールがリリースされることを期待しています。しかし現時点ではBluespec SystemVerilogをLSI設計に適用するためにはBluespec社のシミュレーターやコンパイラを使用する必要があります。

この記事をご覧になり、Bluespec SystemVerilogの詳細情報を確認したい方は、Bluespec社のWebサイト(http://www.bluespec.com/)をご参照いただければ幸いです。SupportページからリンクされているWikiやForumには、ソースコードやリファレンスガイドなどの数多くの情報が公開されています。

サイバネットシステムでは、大学などでの教育、研究用途には無償でBluespec社のツールのライセンスを提供しています。企業向けにも無償の評価版を用意しています。