LSI設計とは

Bluespecはプログラミング言語Bluespec SystemVerilogを使用したLSI設計のための統合環境です。通常、プログラミング言語はソフトウエアを作るために使用されており、LSI設計のためのプログラミング言語と聞いてもイメージがわきにくいと思います。また、「LSIって何?」という読者のためにも、LSI設計の歴史から簡単におさらいしたいと思います。

LSIとはLarge Scale Integrationの略で、大規模集積回路と訳されます。一般的には半導体チップ、ICなどと呼ばれることの多い電子部品の中で、膨大な数の素子を1個の部品に入れ込んで高機能を実現したものの総称です。LSIの有名なものとしては、Intel社のCore 2 Duoなどのプロセッサなどがあり、LSIはパソコンや携帯電話など、ほとんどの電子機器には欠かせない存在です。つまり、LSIというのは皆さんも写真などで見たことがある、電子機器の中に入っている黒くて四角いパーツのことです。

さて、このLSIはソフトウエアと異なり実体を伴う「物」であるため、設計するには形や材料などを決めていくという作業が必要になります。この作業は、家を設計するために設計図を描くことをイメージするとわかりやすいでしょう。

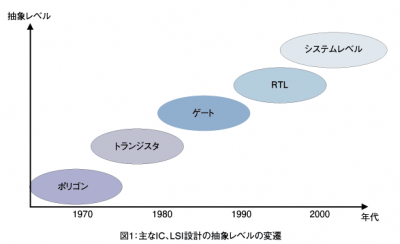

ただしLSIの設計図には兆のオーダのポリゴンを描く必要があり、家と同じようなCAD(Computer Aided Design)を使用して設計することは現実的ではありません。集積度が上がってLSIという用語ができる以前から設計効率を上げるために、いくつかのポリゴンを組み合わせた機能(トランジスタ)単位で設計するような設計のパラダイムシフトを繰り返してきました。このパラダイムシフトを起こす中心として発達してきたのが、LSI設計を中心とする電気回路のためのCADであるEDA(Electronic Design Automation)ツールです。

現在のLSI設計は、RTL(Resister Transfer Level)と言われる抽象レベルを使用することが主流です。それ以前は回路図CADを使用した図形描画によって設計していましたが、RTLへ移行することでテキストベースの設計が可能になりました。

そのRTLを設計するために使用するプログラミング言語がHDL(Hardware Description Language:ハードウエア記述言語)と呼ばれており、Verilog HDLやVHDLなどの種類があります。これらVerilog HDLやVHDLなどで書かれたLSIの設計図(実際には図ではなくテキストですが)から、EDAツールを使用することで半自動的にポリゴンの作成までを行い、LSIを開発していきます。

近年注目されてきたシステムレベル設計

携帯電話は、従来の通話だけの機能から、インターネット接続機能や、ワンセグ視聴機能などが追加され高性能になってきたにも関わらず、大きさはほとんど変わりません。また、以前のスーパーコンピュータ並みの演算性能を小型のPCやゲーム機で実現することができるようになりました。これらのほとんどはLSIの高集積化によって、従来は複数個で実現していた機能を1チップに収めることができるようになったり、高速化、低消費電力化できることを最大限いかした結果によるものです。

このように1チップ内に詰め込むことのできる機能が多くなることは、LSI設計規模が増大することを意味します。現在、LSI設計において「設計生産性危機」と呼ばれる、設計規模の増大のペースに設計効率改善のペースが追いつかないことが原因となる、開発期間の長期化、品質の低下が起こっており、再度パラダイムシフトを起こす必要があると考えられています。

現在のRTLよりも高い抽象レベルはシステムレベル、もしくはESL(Electronic System Level:電子システムレベル)と呼ばれており、このシステムレベル設計への移行が期待されています。

- この記事のキーワード