仮想化にも有効なセキュリティー機能、インテル TXT

仮想化にも有効なセキュリティー機能、インテル TXT

情報ネットワークが急速な発展を遂げる中、それとともに情報漏えいや個人情報の流出が社会問題になっている。実際に2007年あたりから全世界でマルウェア等による被害は急激に増えており、サーバーに対するセキュリティー強化は今や最も対策を講じる必要のある要素の1つだ。

VT-xやVT-dによるVM間のアドレス空間の分離は、セキュリティーという観点からも非常に有効である。しかしHyper-JackingやRoot-Kit等のマルウェアからの防御として考えるとさらに対策を施す必要がある。インテルでは、「インテル Xeon プロセッサー」(以下Xeon) 5600番台からインテル TXT(Trusted eXecution Technology)というセキュリティー強化を目的とした機能を追加している。インテル TXTはハードウエア・レベルのセキュリティー機能でマルウェアによる不正な攻撃を防御するものである。

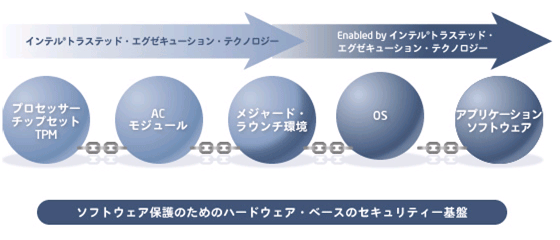

インテル TXTは、TPM(Trusted Platform Module)とAC(Authenticated Code)モジュールを核とした技術である。TPMはISOとIECの承認を受けたセキュリティー・チップで、ハッシュ関数で演算した暗号化鍵を生成、格納し、ACモジュールはCPU内部だけで動作する非常に容量の小さいコードで構成されており、BIOSコードやOS、ハイパーバイザーが実行される前にこれらのコードが信頼できるものであるかを検査する。

インテル TXTはこのTPMとACモジュールを用いてTrust Chainsを形成する。例えばシステムの起動からVMMの起動までを考えると、通常まずCPUはBIOSコード実行、システムの初期化を経てVMMのローディングに至る。インテル TXTはこの一連の処理実行にあたり、それが信頼できるものであるかどうかを検査し、信頼できるものであることが確認できなければ次の処理に移行しない。これがTrust Chainsの考え方である。ソフトウエアが悪意をもって改ざんされていないかをハードウエア・レベルで検査することによって、インテル TXTはより強固なセキュリティーを提供することができる。

|

|

| 図4:インテル TXTの概念図 |

ミッション・クリティカル・サーバーに求められるRAS機能

RASはReliability(信頼性)、Availability(可用性)、Serviceability(保守性)の頭文字を取った略称である。これらは、主に「ミッション・クリティカル・サーバー」と呼ばれる高い信頼性を要求されるサーバーで必要となる用件だと言われている。「インテル Itanium プロセッサー」(以下、Itanium)は、まさにこういった用途を想定して開発されたプロセッサーである。一方、Xeonは設計思想がItaniumと違い、デスクトップ・パソコン用のプロセッサー・コアが設計の起点で、それにRAS機能を追加してきている。

従って、ItaniumはXeonよりも強固なRAS機能を有している。以下では、Xeon 7500番台を中心とするRAS機能について説明する。Xeon 7500番台で特筆すべきRAS機能はMCA(Machine Check Architecture)リカバリだが、これについては次の項にまとめたのでそちらを見ていただきたい。

RAS機能の最も基本的なものが、パリティとECC(Error Check and Correct)である。パリティはエラー検出が可能、ECCで最も一般的なSEC-DED(Single Error correct – Double Error Detect)は1bitの誤り訂正、2bitのエラー検出が可能である。当然、パリティに比べてアルゴリズムが複雑な分、処理に時間を要する。

従って、プロセッサーの中でエラー保護している部分は、場所に応じてパリティとSEC-DEDが採用されている。DIMMもSEC-DEDが基本だが、ECCの冗長bitを拡張し、x4/x8のSDDC+1(Single Device Data Correction plus 1bit error correction)も可能にしている。「x4 SDDC」は連続した4bit以下、「x8 SDDC」は連続した8bit以下の誤り訂正が可能なECCである。

つまり、DIMMのDRAMが4bitデータ幅のものであれば「x4 SDDC」、8bitデータ幅のものであれば「x8 SDDC」によって、DIMM上のDRAMが1石破損して機能しない状況に陥ったとしても、そのDRAMを切り離して動作することができるのである。

「SDDC+1」というのは、DRAMを1石切り離した状態でさらに残りのDRAMで1bit誤りが発生しても訂正することができる。DIMMにかかわるRAS機能としては、さらにミラーリング、スペアリングという機能もある。おのおのDIMMを冗長構成にするものではあるが、RAS機能としては非常に有効な機能である。

また、前回紹介したQPI(Quick Path Interconnect)にもさまざまな保護機能がある。まず基本はCRC(Cyclic Redunduncy Check)である。QPIはシリアル・バスなので、データ・ストリームで発生するバースト誤りの検出にも有効な方法だ。QPIバス上でエラーを検出した場合にはパケット単位でのリトライを行う。

さらには、QPIはforwarded clock方式を採用しているのでクロック・レーンが存在するが、このクロック・レーンに障害が発生した場合にはデータ・レーンをクロック・レーンにフェイル・オーバーする機能、データ・レーンに障害が発生した場合にはデータ・レーンを半分、1/4に縮退して動作するレーン・リダクション機能と2重、3重の保護機能を用意している。