仮想化を高速化するための機能

今回はハードウエア仮想化の高速化や安全性を高めるためのCPUの仕組みについて、紹介していきます。

仮想環境下では、利用状況によってホストOSとゲストOSが切り替わります。つまり「第1回:ハードウエア仮想化技術を知る!(http://www.thinkit.co.jp/article/125/1/)」で紹介した「VM Entry(VM RUN)」と「VM Exit」によるVMM遷移です。しかしVMM遷移が頻繁に発生したり長く続いたりすると、CPUが仮想化に対応していても、性能が低下してしまいます。

特にその中でもページフォールトによるVMM遷移がボトルネックになりやすく、パフォーマンスに大きく影響します。ページフォールトとは、アプリケーションがメインメモリに上にないページにアクセスしようとした時に、ハードディスクなどの補助メモリから読み込んだページをメインメモリに読み込む割り込み処理です。

最新のCPUは、こうしたページフォールトの発生を押さえたり、一度利用したデータをバッファーにため込むことで、仮想化をより効率的にえるようにするための仕組みを備えています。まずは、その仕組みについて説明しましょう。

ボトルネックを解消する新技術

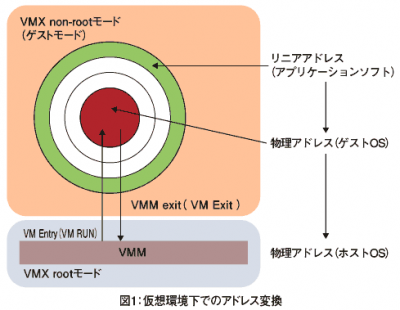

ハードウエア仮想化では、図1に示すように、アプリケーションがゲストOSを判別するためのリニアアドレス、ゲストOSの物理アドレス、ホストOSの物理アドレスの3つのアドレスが利用されており、それぞれ変換しながら処理を行っています。

アプリケーションがリニアアドレスを参照する時に、ページフォールトが発生してしまうと、VM Exitとなり、VMX non-rootモードからVMX rootモードに遷移してしまいます。これが頻繁に発生すると、ボトルネックとなりパフォーマンスが低下します。

そこで、アプリケーションでページフォールトが発生してもVM Exitが発生しないようにするための仕組みが用意されました。1つがIntelのEMT(Extended Memory Table)、もう1つがAMDのNPT(Nested Page Table)です。原稿執筆時点(2008年8月現在)ではNPTは実装済みですが、EMTはまだ実装されていません。

基本的にEMTとNPTの考え方は同じです。従来変換テーブルとして、ゲストOSのリニアアドレスとゲストOSの物理アドレスの対応表を持っていましたが、それにゲストOSの物理アドレスとホストOSの物理アドレスの対応表を1段追加しました。

これらのテーブルはゲストOS環境下で参照できるため、VM ExitでホストOSに遷移する必要がなくなり、ボトルネックを解消できます。この威力は大変大きく、これがなければCPUの仮想化は十分でないと言う人もいるほどです。

もう1つ、仮想化環境を高速化させるための技術として、TLB(Translation Look-aside Buffer)を効率的に使う技術があります。IntelではVPID(Virtual-processor ID)、AMDではTagged TLBと呼ばれています。

TLBとは、アドレス変換を高速化するためのバッファーです。テーブルによるアドレス変換では、一度アドレス変換が行われると、2度目以降はテーブルではなく変換履歴を参照して変換します。つまり、アドレス変換のキャッシュメモリーのようなものです。

しかし、VM Exitが発生するとこれらのキャッシュがフラッシュ(無効化)されてしまうため、それ以降にアドレス変換する時にまたテーブルから参照しなければなりません。これがゲストOS上の性能を低下させる原因になっていました。

そこで、VPIDやTagged TLBでは、VM Exitが発生してもTLBがフラッシュされないようにすることで、高速化をはかっています。

上記で紹介したEPTとNPT、VPIDとTagged TLBは、まだ実装されていないものもありますが、各社とも2008年の末ごろに出荷する最新のCPUには搭載していくと予想されます。今後、仮想環境でも物理環境と同じようにベンチマークによる性能の競争がくり広げられるようになるでしょう。

しかし、導入する立場にとって大事なのは、何をどういった環境下で検証した性能評価なのかを見極めることです。メーカーのベンチマークの数値のみに振り回されることなく、実際に導入する環境でどのような性能が求められているのかを考慮して製品を選ぶ必要があります。

次は、I/Oの仮想化について解説しましょう。

- この記事のキーワード