XeonプロセッサD製品ファミリの概要

2015年3月10日、インテルは、Broadwellコアを採用し、シリーズ初となるSoC構成のXeon プロセッサD製品ファミリー(以下Xeon Dと表記します)を発表しました(図1)。SoC(System on a Chip)とは、プロセッサと周辺回路などを1つのパッケージにまとめた半導体デバイスの構成方法の1つで、主にフットプリント(基板上の占有面積)を押さえるために作られました。そもそもは、携帯電話などの小型機器を高機能化する過程で出てきたものです。現在では、タブレットやスマートフォンなどに使われるプロセッサは例外なくSoCです。また、PC用のプロセッサも、かつてはチップセットなどと呼ばれた周辺回路をまとめたチップと組み合わせることが普通でしたが、最近では、多くの機能がCPUパッケージに構成されつつあります。

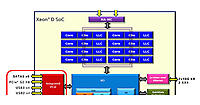

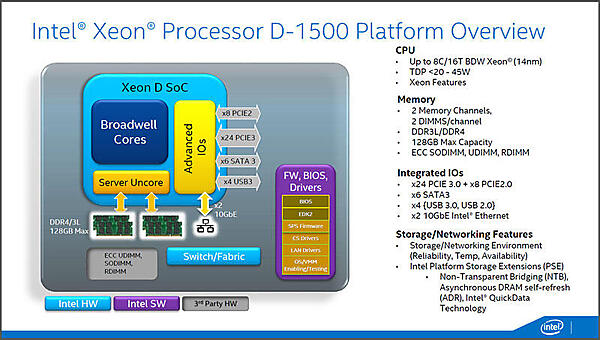

SoCの明確な定義はありませんが、基本的にはコンピュータを構成する大半の回路を1つのパッケージに集積したものをいいます。狭義には、1つのダイ(半導体を構成するシリコン)にすべての回路を統合したものをいいますが、1つのパッケージに複数のチップを入れたマルチチップキャリア構成でもSoCと呼ぶことがあります。また、プロセッサが小規模な回路では、RAMやROMを統合したものものありますが、SoCでもシステム構成を柔軟にするため、RAMやROMは外付けとなっているのが普通です。Xeon Dは、従来外付けチップとして必要だったPCH(Platform Control Hub)を内蔵していて、外部チップセットが不要になっています(図2)。

図2:Xeonプロセッサ D-1500プラットフォームの概要。Xeon Dは、周辺回路を統合していて、内部にメモリコントローラーや10Gビットイーサーネット、USB、SATA、PCI Expressといったインターフェイスを持つ(出典:インテル)。

Xeonシリーズは、インテルのサーバー向けのCPUです。基本的なCPUの実装(これをマイクロアーキテクチャといいます)は、パソコンに使われているCPUと同じですが、サーバー向けに、キャッシュメモリが増強されており、エラーなどに対して耐性を持つフォールトトレラント機能などが追加されています。また、最近のPCでは、表示のためのGPUを統合するのが標準ですが、必ずしもGUIアプリケーションを動かすわけではないサーバー向けプロセッサでは、GUIを統合していない製品も少なくありません。

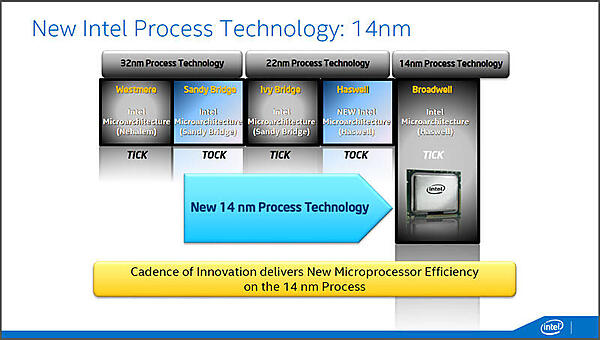

インテルのパソコン用のプロセッサは、ここ何年かは「マイクロアーキテクチャ」を更新する「Tick」と、製造プロセスを変更する「Tock」を毎年交互に行うという形で製品を発表しています(図3)。これに対してサーバー向けのプロセッサは、パソコン向けのプロセッサが登場したあと、これを改良して製品を設計しているため、製品発表のタイミングがパソコン用のものよりも後に行われるのが普通です。一般的にサーバーは、パソコンなどに比べると、検証などで導入に時間がかかり、パソコンの様に毎年新製品が出ることが歓迎されているわけではありません。また、一度導入すると、一定の期間は製品を更新することなくシステムが稼働するため、製品更新のサイクルも長くなるのが普通です。これは、大規模であるほど、システムの重要性が高いほど長くなります。このため、Xeonシリーズも最上位のプロセッサよりも下位のプロセッサから先に製品が更新されていきます。

今回発表されたXeon Dのプロセッサコアは、Broadwellというコード名を持ち、部分のマイクロアーキテクチャはHaswellです。パソコン用の第5世代Coreアーキテクチャと基本的な部分は同じものを採用しています。構成的には、Haswellマイクロアーキテクチャを14nmプロセスで製造したプロセッサです。

ただし、マイクロアーキテクチャは同一ですが、Xeon Dと第5世代CoreプロセッサのCPUコアは同一のものではありません。

このXeon Dシリーズは、従来の3系列のXeonとは違う製品系列として新規に投入されたものです。インテルのサーバープロセッサには、これまでXeon系列(3シリーズ)とAtom C2000シリーズがありました。今回発表されたXeon Dプロセッサは、Atom C2000とXeonシリーズの間に位置するものです。

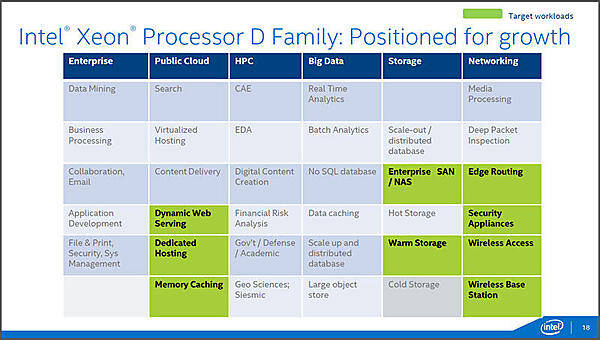

Atomプロセッサコアを使うC2000とXeonでは、性能差が大きく、その間を埋めるものが必要でした。インテルは、新規用途、市場を開拓するため、今回Xeon Dプロセッサを企画したといいます。主な用途としては、シングルスレッド性能的にはAtomプロセッサコアでは対応が難しい分野や、クラウドサービスやインターネットサーバーシステムのうち、ネットワークに近い、俗に言う「エッジ」部分、あるいは通信システム関連、ストレージシステムといった分野を想定しているようです(図4)。

SoCであることで、フットプリントが小さくなるため、Xeon Dプロセッサを採用するシステムではボード面積が小さくなり、従来のXeonプロセッサを採用した製品に比べると、同じ体積により多くのシステムボードを淹れることができるようになります。あるいは、機器自体を小型化することが可能です。

サーバーといっても、さまざまな用途があり、プロセッサは、「マルチスレッド性能」、「シングルスレッド性能」、「実装密度」などの特性を持ちます。Xeon Dプロセッサは、このうち「マルチスレッド性能」はそれほど高くありませんが、上位のXeonプロセッサと比較すると「実装密度」を高くできるプロセッサです。

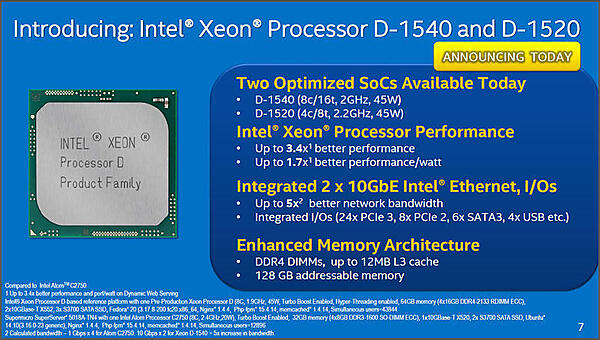

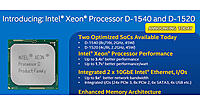

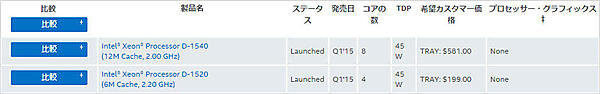

今回の発表では、D-1540とD-1520の2つのプロセッサが具体的な製品として発表されました(図5)。インテルによれば、Xeon Dは、この2つだけということはなく、今後製品が追加、あるいは更新される可能性があるということです。

図5:Xeon DのSKU。Xeon Dは、具体的な製品としてはD-1540とD-1520が最初に出荷される。違いはコア数とクロック周波数、LLC容量など。ちなみにGPUは搭載されていない(出典:インテル)。

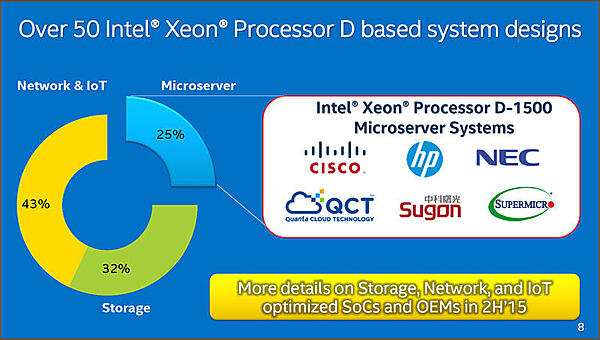

2つのプロセッサは仕様としてはほぼ同じで、CPUコアの数(D-1540は8コア、D-1520は4コア。以下同様)キャッシュサイズ(12Mバイト、6Mバイト)とCPUクロック(2ギガヘルツ、2.2ギガヘルツ)という違いがあります。発売は2015年の第1四半期で、すでに50を越えるメーカーが、Xeon Dを使った製品の設計を開始しているとのことです。また、このうち25%は、いわゆるマイクロサーバー製品だといいます(図6)。その他は、ストレージ、ネットワークおよびIoT関連です。なお、マイクロサーバー以外の製品に関しては、今年後半に詳細がはっきりするとのこと。

SoCの特徴

次にSoCとしてのXeon Dを見ていくことにしましょう。Xeon Dは、コンピュータを構成する部品のうち、RAMやROM以外の部分をプロセッサパッケージに統合しています。従来のプロセッサでいえば、PCHに相当する機能が含まれています。

また、通信用途を想定して10Gビットのイーサネットインターフェイスを2つ搭載しています。ただし、内蔵しているのは、MAC(Media Access Control)層までなので、外部にPHYと呼ばれる部品(仕様に合わせて電気信号を変換する)を付ける必要があります。もっとも、単純に10Gビットイーサーネットといってもケーブルの種類などに複数(たとえば銅線や光ファイバなど)があるため、一般にPHYは外付け部品として目的に合わせて設計するのが普通です。

外部のデバイスとはPCI Express(Gen2およびGen3)、USB(2および3)などで接続を行います。このほかにストレージデバイス接続用のSATA(Serial ATA)やLegacy IOと呼ばれるBIOS ROM(BIOS用フラッシュメモリ)や温度測定チップなどを接続するためのインターフェイスが搭載されています。

メインメモリは、DDR4またはDDR3Lで、最大接続メモリ容量は128Gバイトです。メモリコントローラーが2チャンネル内蔵されているため、CPUに直接DIMMを接続でき、1つのチャンネルには最大で2つのDIMMを接続できるため、DIMMの最大接続数は4つになります。

Xeon Dは、大きくコア部分とI/O回路を統合したIIO(Integrated I/O)および、Serial ATAやUSB、PCIe Gen2などといったI/O関係のデバイスの制御を行う、統合PCH(Platform Controller Hub)から構成されます。このうちPCH部分は、従来外付けのチップセットとして別パッケージだったものを統合したものです。ただし、Xeon Dの最初の製品である1520と1540の場合、PCH部分は、CPUと同じ「ダイ」(シリコンなどからなる半導体チップ)ではなく、別に製造されたダイをパッケージ内で接続するMCC(Multi Chip Carrier)と呼ばれる方式です。ただし、これはあくまでも製造上のもので、外部からみれば、機能的には1つのパッケージにCPUやPCHが統合されているように見えます。

IIOは、CPUと同じダイの上に乗っていて、ここは、新規に設計された部分です。このため、ここにある機能については、PCI Express 3.0のCRC機能などのように、新規の機能となるものがあります。

SoCとしてのXeon Dは、既存のPCHと新規設計のSoCコアを組み合わせて作られたプロセッサです。実際にIIO部分にPCI Express 3.0が搭載されているほか、10Gビットのイーサネットインターフェイスなども搭載されているため、Xeon初、あるいはBroadwell系最初のSoCといっても間違いではありません。PCHをMCCで搭載したのは、開発期間を短縮するためだと思われます。Xeon系では、PC用のCPUより厳密な動作が求められます。新規設計では、新たに問題が発生する可能性もあります。だとすると、一部でも既存の実績のあるチップを使うことで、新規に発生する問題を抑えることが可能です。また、既存のチップをそのまま使えば、設計の時間を短縮することも可能だからです。

--次回に続く